# Nonvolatile, I<sup>2</sup>C-Compatible 256-Position, Digital Potentiometer

# AD5259

#### FEATURES

Nonvolatile memory maintains wiper settings 256-position Thin LFCSP-10 (3 mm x 3 mm x 0.8 mm) package Compact MSOP-10 (3 mm × 4.9 mm x 1.1mm) package  $l^2C^{\circ}$ -compatible interface  $V_{\text{LOGIC}}$  pin provides increased interface flexibility End-to-end resistance 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$

Resistance tolerance stored in EEPROM (0.1% accuracy)

Power-on EEPROM refresh time < 1ms

Software write protect command

Address Decode Pin AD0 and Pin AD1 allow

4 packages per bus 100-year typical data retention at 55°C

Wide operating temperature –40°C to +85°C

3 V to 5 V single supply

### APPLICATIONS

LCD panel V<sub>COM</sub> adjustment LCD panel brightness and contrast control Mechanical potentiometer replacement in new designs Programmable power supplies RF amplifier biasing Automotive electronics adjustment Gain control and offset adjustment Fiber to the home systems Electronics level settings

#### **GENERAL DESCRIPTION**

The AD5259 provides a compact, nonvolatile LFCSP-10 (3 mm  $\times$  3 mm) or MSOP-10 (3 mm  $\times$  4.9 mm) packaged solution for 256-position adjustment applications. These devices perform the same electronic adjustment function as mechanical potentiometers<sup>1</sup> or variable resistors, but with enhanced resolution and solid-state reliability.

The wiper settings are controllable through an I<sup>2</sup>C-compatible digital interface that is also used to read back the wiper register and EEPROM content. Resistor tolerance is also stored within EEPROM, providing an end-to-end tolerance accuracy of 0.1%.

A separate  $V_{\text{LOGIC}}$  pin delivers increased interface flexibility. For users who need multiple parts on one bus, Address Bit AD0 and Address Bit AD1 allow up to four devices on the same bus.

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

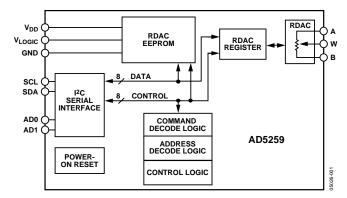

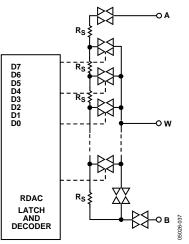

### FUNCTIONAL BLOCK DIAGRAMS

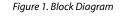

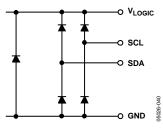

Figure 2. Block Diagram Showing Level Shifters

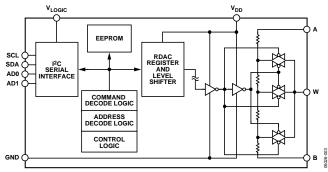

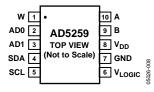

#### **CONNECTION DIAGRAM**

Figure 3. Pinout

$^{\rm 1}$  The terms digital potentiometer, VR (variable resistor), and RDAC are used interchangeably.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

© 2005 Analog Devices, Inc. All rights reserved.

## TABLE OF CONTENTS

| Specifications                               | $I^2$ |

|----------------------------------------------|-------|

| Electrical Characteristics                   |       |

| Timing Characteristics5                      |       |

| Absolute Maximum Ratings                     |       |

| ESD Caution                                  |       |

| Pin Configuration and Function Descriptions7 |       |

| Typical Performance Characteristics          |       |

| Test Circuits                                |       |

| Theory of Operation14                        |       |

| Programming the Variable Resistor14          |       |

| Programming the Potentiometer Divider14      |       |

| I <sup>2</sup> C-Compatible Interface15      | D     |

| Writing15                                    |       |

| Storing/Restoring15                          | C     |

| Reading                                      |       |

### **REVISION HISTORY**

| 7/05 — Rev. 0 to Rev. A                                  |           |

|----------------------------------------------------------|-----------|

| Added 10-Lead LFCSP                                      | Universal |

| Changes to Features Section and                          |           |

| General Description Section                              | 1         |

| Changes to Table 1                                       |           |

| Changes to Table 2 and Added Figure 4                    | 5         |

| Changes to Table 4                                       | 7         |

| Changes to Figure 27 Caption                             |           |

| Changes to Theory of Operation Section                   | 14        |

| Changes to I <sup>2</sup> C-Compatible Interface Section |           |

| Changes to Table 5                                       | 16        |

| Changes to Multiple Devices on One Bus Section           |           |

| Updated Figure 49 Caption                                |           |

| Changes to Ordering Guide                                |           |

$2/05-{\rm Revision}$ 0: Initial Version

| 3 | I <sup>2</sup> C-Compatible Format16                     |

|---|----------------------------------------------------------|

| 3 | Generic Interface                                        |

| 5 | Write Modes16                                            |

| 6 | Read Modes17                                             |

| 6 | Store/Restore Modes                                      |

| 7 | Tolerance Readback Modes18                               |

| 8 | ESD Protection of Digital Pins and Resistor Terminals 19 |

| 3 | Power-Up Sequence19                                      |

| 4 | Layout and Power Supply Bypassing19                      |

| 4 | Multiple Devices on One Bus 19                           |

| 4 | Evaluation Board 19                                      |

| 5 | Display Applications                                     |

| 5 | Circuitry 20                                             |

| 5 | Outline Dimensions                                       |

| 5 | Ordering Guide21                                         |

### **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{DD}} = V_{\text{LOGIC}} = 5 \text{ V} \pm 10\% \text{ or } 3 \text{ V} \pm 10\%; V_{\text{A}} = V_{\text{DD}}; V_{\text{B}} = 0 \text{ V}; -40^{\circ}\text{C} < T_{\text{A}} < +85^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 1.

| Parameter                                         | Symbol                                                           | Conditions                                 | Min  | Typ1   | Max             | Unit   |

|---------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|------|--------|-----------------|--------|

| DC CHARACTERISTICS:<br>RHEOSTAT MODE              |                                                                  |                                            |      |        |                 |        |

| Resistor Differential Nonlinearity                | R-DNL                                                            | $R_{WB}$ , $V_A$ = no connect              |      |        |                 | LSB    |

| 5 kΩ                                              |                                                                  |                                            | -1   | ±0.2   | +1              |        |

| 10 kΩ                                             |                                                                  |                                            | -1   | ±0.1   | +1              |        |

| 50 kΩ/100 kΩ                                      |                                                                  |                                            | -0.5 | ±0.1   | +0.5            |        |

| Resistor Integral Nonlinearity                    | R-INL                                                            | $R_{WB}$ , $V_A$ = no connect              |      |        |                 | LSB    |

| 5 kΩ                                              |                                                                  |                                            | -4   | ±0.3   | +4              |        |

| 10 kΩ                                             |                                                                  |                                            | -2   | ±0.2   | +2              |        |

| 50 kΩ/100 kΩ                                      |                                                                  |                                            | -1   | ±0.4   | +1              |        |

| Nominal Resistor Tolerance                        | $\Delta R_{AB}$                                                  | $T_A = 25^{\circ}C, V_{DD} = 5.5 V$        | -30  |        | +30             | %      |

| Resistance Temperature Coefficient                | (ΔR <sub>AB</sub> x 10 <sup>6</sup> )/<br>(R <sub>AB</sub> x ΔT) | Code = 0x00/0x80                           |      | 500/15 |                 | ppm/°C |

| Total Wiper Resistance                            | RwB                                                              | Code = 0x00                                |      | 75     | 350             | Ω      |

| DC CHARACTERISTICS:<br>POTENTIOMETER DIVIDER MODE |                                                                  |                                            |      |        |                 |        |

| Differential Nonlinearity                         | DNL                                                              |                                            |      |        |                 | LSB    |

| 5 kΩ                                              |                                                                  |                                            | -1   | ±0.2   | +1              |        |

| 10 kΩ                                             |                                                                  |                                            | -0.5 | ±0.1   | +0.5            |        |

| 50 kΩ/100 kΩ                                      |                                                                  |                                            | -0.5 | ±0.2   | +0.5            |        |

| Integral Nonlinearity                             | INL                                                              |                                            |      |        |                 | LSB    |

| 5 kΩ                                              |                                                                  |                                            | -1   | ±0.2   | +1              |        |

| 10 kΩ                                             |                                                                  |                                            | -0.5 | ±0.1   | +0.5            |        |

| 50 kΩ/100 kΩ                                      |                                                                  |                                            | -0.5 | ±0.1   | +0.5            |        |

| Full-Scale Error                                  | Vwfse                                                            | Code = 0xFF                                |      |        |                 | LSB    |

| 5 kΩ                                              |                                                                  |                                            | -7   | -3     | 0               |        |

| 10 kΩ                                             |                                                                  |                                            | -4   | -1.5   | 0               |        |

| 50 kΩ/100 kΩ                                      |                                                                  |                                            | -1   | -0.4   | 0               |        |

| Zero-Scale Error                                  | V <sub>WZSE</sub>                                                | Code = 0x00                                |      |        |                 | LSB    |

| 5 kΩ                                              |                                                                  |                                            | 0    | 2.5    | 4               |        |

| 10 kΩ                                             |                                                                  |                                            | 0    | 1      | 3               |        |

| 50 kΩ/100 kΩ                                      |                                                                  |                                            | 0    | 0.2    | 0.5             |        |

| Voltage Divider Temperature<br>Coefficient        | (ΔV <sub>W</sub> x 10 <sup>6</sup> )/<br>(V <sub>W</sub> x ΔT)   | Code = 0x00/0x80                           |      | 60/5   |                 | ppm/°C |

| RESISTOR TERMINALS                                |                                                                  |                                            |      |        |                 |        |

| Voltage Range                                     | V <sub>A, B, W</sub>                                             |                                            | GND  |        | V <sub>DD</sub> | V      |

| Capacitance A, B                                  | Са, в                                                            | f = 1 MHz, measured to GND, code = 0x80    |      | 45     |                 | pF     |

| Capacitance W                                     | Cw                                                               | f = 1 MHz, measured to GND,<br>code = 0x80 |      | 60     |                 | pF     |

| Common-Mode Leakage                               | Ісм                                                              | $V_A = V_B = V_{DD}/2$                     |      | 10     |                 | nA     |

| Parameter                         | Symbol            | Conditions                                                                                          | Min              | Typ <sup>1</sup> | Max             | Unit  |

|-----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|-------|

| DIGITAL INPUTS AND OUTPUTS        |                   |                                                                                                     |                  |                  |                 |       |

| Input Logic High                  | VIH               |                                                                                                     | $0.7 \times V_L$ |                  | $V_{L} + 0.5$   | V     |

| Input Logic Low                   | VIL               |                                                                                                     | -0.5             |                  | $0.3 	imes V_L$ | V     |

| Leakage Current                   | lı∟               |                                                                                                     |                  |                  |                 | μΑ    |

| SDA, AD0, AD1                     |                   | $V_{IN} = 0 V \text{ or } 5 V$                                                                      |                  | 0.01             | ±1              |       |

| SCL – Logic High                  |                   | $V_{IN} = 0 V$                                                                                      | -2.5             | -1.3             | +1              |       |

| SCL – Logic Low                   |                   | $V_{IN} = 5 V$                                                                                      |                  | 0.01             | ±1              |       |

| Input Capacitance                 | CIL               |                                                                                                     |                  | 5                |                 | рF    |

| POWER SUPPLIES                    |                   |                                                                                                     |                  |                  |                 |       |

| Power Supply Range                | V <sub>DD</sub>   |                                                                                                     | 2.7              |                  | 5.5             | V     |

| Positive Supply Current           | IDD               |                                                                                                     |                  | 0.1              | 2               | μΑ    |

| Logic Supply                      | VLOGIC            |                                                                                                     | 2.7              |                  | 5.5             | V     |

| Logic Supply Current              |                   | $V_{IH} = 5 V \text{ or } V_{IL} = 0 V$                                                             |                  | 3                | 6               | μΑ    |

| Programming Mode Current (EEPROM) | LOGIC(PROG)       | $V_{IH} = 5 V \text{ or } V_{IL} = 0 V$                                                             |                  | 35               |                 | mA    |

| Power Dissipation                 | P <sub>DISS</sub> | $V_{\text{IH}} = 5 \text{ V or } V_{\text{IL}} = 0 \text{ V}, V_{\text{DD}} = 5 \text{ V}$          |                  | 15               | 40              | μW    |

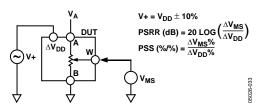

| Power Supply Rejection Ratio      | PSRR              | $V_{DD} = +5 V \pm 10\%$ , code = 0x80                                                              |                  | ±0.005           | ±0.06           | %/%   |

| DYNAMIC CHARACTERISTICS           |                   |                                                                                                     |                  |                  |                 |       |

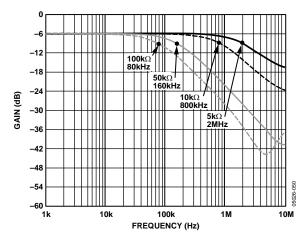

| Bandwidth –3 dB                   | BW                | Code = 0x80                                                                                         |                  |                  |                 |       |

|                                   |                   | $R_{AB} = 5 \ k\Omega$                                                                              |                  | 2000             |                 | kHz   |

|                                   |                   | $R_{AB} = 10 \ k\Omega$                                                                             |                  | 800              |                 | kHz   |

|                                   |                   | $R_{AB} = 50 \ k\Omega$                                                                             |                  | 160              |                 | kHz   |

|                                   |                   | $R_{AB} = 100 \ k\Omega$                                                                            |                  | 80               |                 | kHz   |

| Total Harmonic Distortion         | THDw              | $\begin{split} R_{AB} &= 10 \ k\Omega, \ V_A = 1 \ V \ rms, \\ V_B &= 0, \ f = 1 \ kHz \end{split}$ |                  | 0.01             |                 | %     |

| V <sub>w</sub> Settling Time      | ts                | $R_{AB} = 10 \text{ k}\Omega$ , $V_{AB} = 5 \text{ V}$ ,<br>±1 LSB error band                       |                  | 500              |                 | ns    |

| Resistor Noise Voltage Density    | en_wb             | $R_{WB} = 5 k\Omega, f = 1 kHz$                                                                     |                  | 9                |                 | nV/√⊦ |

$^{_{\rm 1}}$  Typical values represent average readings at 25°C and  $V_{\text{DD}}$  = 5 V.

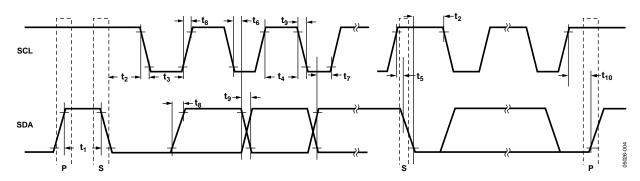

### **TIMING CHARACTERISTICS**

$V_{DD} = V_{LOGIC} = 5 V \pm 10\%$  or  $3 V \pm 10\%$ ;  $V_A = V_{DD}$ ;  $V_B = 0 V$ ;  $-40^{\circ}C < T_A < +85^{\circ}C$ , unless otherwise noted.

#### Table 2.

| Parameter                                                         | Symbol                   | Conditions                                                                                             | Min | Тур | Max | Unit    |

|-------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| I <sup>2</sup> C INTERFACE TIMING<br>CHARACTERISTICS <sup>1</sup> |                          |                                                                                                        |     |     |     |         |

| SCL Clock Frequency                                               | fscl                     |                                                                                                        | 0   |     | 400 | kHz     |

| t <sub>BUF</sub> Bus Free Time Between Stop<br>and Start          | t1                       |                                                                                                        | 1.3 |     |     | μs      |

| $t_{\text{HD};\text{STA}}$ Hold Time (Repeated Start)             | t <sub>2</sub>           | After this period, the first clock pulse is generated.                                                 | 0.6 |     |     | μs      |

| t <sub>LOW</sub> Low Period of SCL Clock                          | t <sub>3</sub>           |                                                                                                        | 1.3 |     |     | μs      |

| thigh High Period of SCL Clock                                    | t4                       |                                                                                                        | 0.6 |     |     | μs      |

| t <sub>su;sTA</sub> Setup Time for Repeated<br>Start Condition    | t₅                       |                                                                                                        | 0.6 |     |     | μs      |

| thd;dat Data Hold Time                                            | t <sub>6</sub>           |                                                                                                        | 0   |     | 0.9 | μs      |

| t <sub>su;DAT</sub> Data Setup Time                               | t <sub>7</sub>           |                                                                                                        | 100 |     |     | ns      |

| t <sub>F</sub> Fall Time of Both SDA and<br>SCL Signals           | t <sub>8</sub>           |                                                                                                        |     |     | 300 | ns      |

| t <sub>R</sub> Rise Time of Both SDA and<br>SCL Signals           | t9                       |                                                                                                        |     |     | 300 | ns      |

| tsu;sto Setup Time for Stop Condition                             | t <sub>10</sub>          |                                                                                                        | 0.6 |     |     | μs      |

| EEPROM Data Storing Time                                          | t <sub>EEMEM_STORE</sub> |                                                                                                        |     | 26  |     | ms      |

| EEPROM Data Restoring Time at<br>Power On <sup>2</sup>            | teemem_restore1          | $V_{\text{DD}}$ rise time dependent. Measure without decoupling capacitors at $V_{\text{DD}}$ and GND. |     | 300 |     | μs      |

| EEPROM Data Restoring Time upon<br>Restore Command <sup>2</sup>   | teemem_restore2          | $V_{DD} = 5 V.$                                                                                        |     | 300 |     | μs      |

| EEPROM Data Rewritable Time <sup>3</sup>                          | teemem_rewrite           |                                                                                                        |     | 540 |     | μs      |

| FLASH/EE MEMORY RELIABILITY                                       |                          |                                                                                                        |     |     |     |         |

| Endurance <sup>4</sup>                                            |                          |                                                                                                        | 100 | 700 |     | kCycles |

| Data Retention <sup>5</sup>                                       |                          |                                                                                                        |     | 100 |     | Years   |

<sup>1</sup> Standard I<sup>2</sup>C mode operation guaranteed by design.

<sup>2</sup> During power-up, the output is momentarily preset to midscale before restoring EEPROM content.

<sup>3</sup> Delay time after power-on PRESET prior to writing new EEPROM data. <sup>4</sup> Endurance is qualified to 100,000 cycles per JEDEC Std. 22 method A117, and is measured at -40°C, +25°C, and +85°C; typical endurance at +25°C is 700,000 cycles. <sup>5</sup> Retention lifetime equivalent at junction temperature (T<sub>2</sub>) = 55°C per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature.

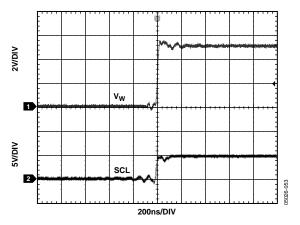

Figure 4. I<sup>2</sup>C Interface Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| Parameter                                                                  | Value                         |

|----------------------------------------------------------------------------|-------------------------------|

| V <sub>DD</sub> , V <sub>LOGIC</sub> to GND                                | –0.3 V to +7 V                |

| V <sub>A</sub> , V <sub>B</sub> , V <sub>W</sub> to GND                    | $GND - 0.3 V, V_{DD} + 0.3 V$ |

| Імах                                                                       |                               |

| Pulsed <sup>1</sup>                                                        | ±20 mA                        |

| Continuous                                                                 | ±5 mA                         |

| Digital Inputs and Output Voltage to GND                                   | 0 V to 7 V                    |

| Operating Temperature Range                                                | -40°C to +85°C                |

| Maximum Junction Temperature<br>(T <sub>JMAX</sub> )                       | 150°C                         |

| Storage Temperature                                                        | –65°C to +150°C               |

| Lead Temperature<br>(Soldering, 10 sec)<br>Thermal Resistance <sup>2</sup> | 300°C                         |

| $\theta_{JA}$ : MSOP-10                                                    | 200°C/W                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1</sup> Maximum terminal current is bounded by the maximum current handling of the switches, maximum power dissipation of the package, and maximum applied voltage across any two of the A, B, and W terminals at a given resistance.

<sup>2</sup> Package power dissipation =  $(T_{JMAX} - T_A)/\theta_{JA}$ .

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

| Table 4. | r in Function Descripti | UIIS                                                                               |

|----------|-------------------------|------------------------------------------------------------------------------------|

| Pin      | Mnemonic                | Description                                                                        |

| 1        | W                       | W Terminal, $GND \le V_W \le V_{DD}$ .                                             |

| 2        | ADO                     | Programmable Pin 0 for Multiple Package Decoding. State is registered on power-up. |

| 3        | AD1                     | Programmable Pin 1 for Multiple Package Decoding. State is registered on power-up. |

| 4        | SDA                     | Serial Data Input/Output.                                                          |

| 5        | SCL                     | Serial Clock Input. Positive edge triggered.                                       |

| 6        | VLOGIC                  | Logic Power Supply.                                                                |

| 7        | GND                     | Digital Ground.                                                                    |

| 8        | V <sub>DD</sub>         | Positive Power Supply.                                                             |

| 9        | В                       | B Terminal, $GND \le V_B \le V_{DD}$ .                                             |

| 10       | А                       | A Terminal, $GND \le V_A \le V_{DD}$ .                                             |

### **Table 4. Pin Function Descriptions**

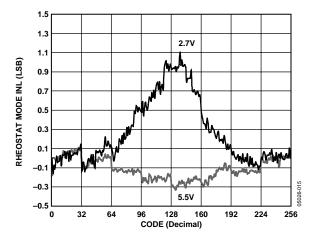

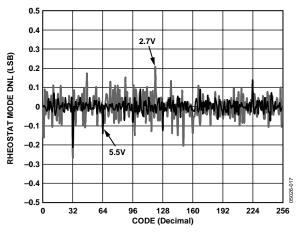

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{DD} = V_{LOGIC} = 5.5 \text{ V}, R_{AB} = 10 \text{ k}\Omega, T_A = +25^{\circ}\text{C}$ ; unless otherwise noted.

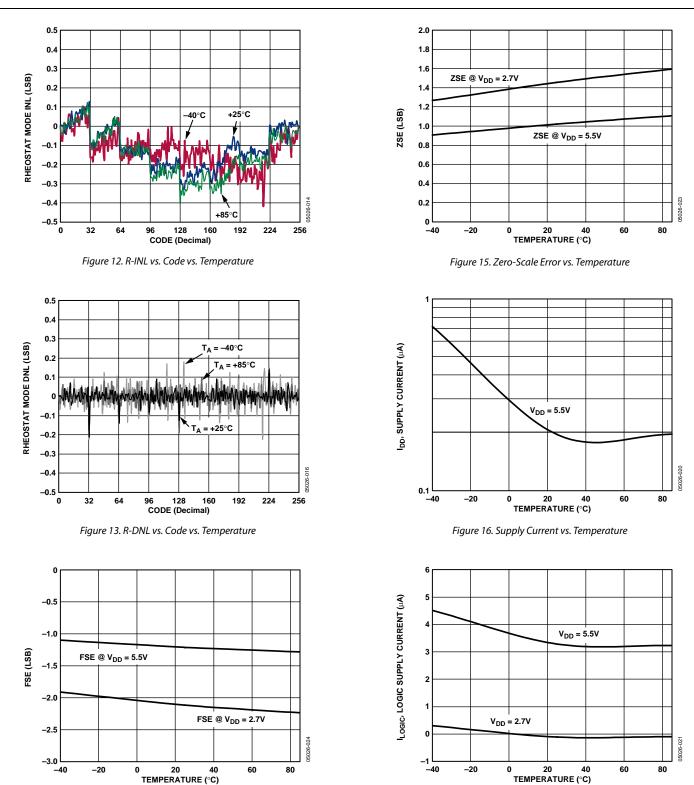

Figure 6. R-INL vs. Code vs. Supply Voltage

Figure 7. R-DNL vs. Code vs. Supply Voltage

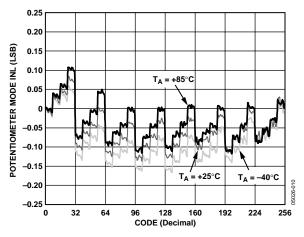

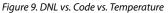

Figure 8. INL vs. Code vs. Temperature

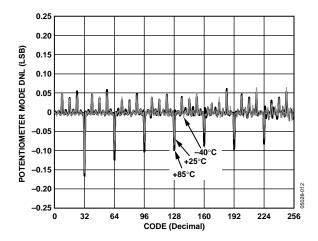

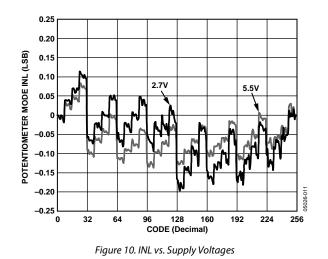

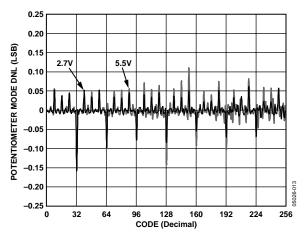

Figure 11. DNL vs. Code vs. Supply Voltage

Figure 14. Full-Scale Error vs. Temperature

Figure 17. Logic Supply Current vs. Temperature vs.  $V_{DD}$

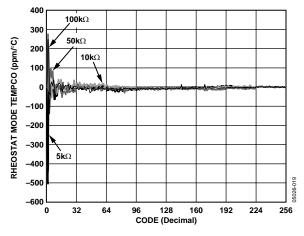

Figure 18. Rheostat Mode Tempco ( $\Delta R_{AB} \times 10^{6}$ )/( $R_{AB} \times \Delta T$ ) vs. Code

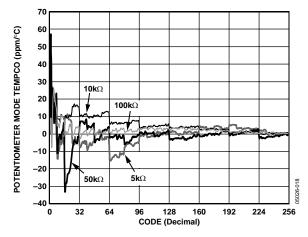

Figure 19. Potentiometer Mode Tempco ( $\Delta V_W \times 10^6$ )/( $V_W \times \Delta T$ ) vs. Code

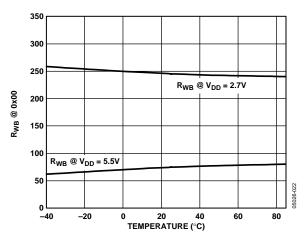

Figure 20. R<sub>WB</sub> vs. Temperature

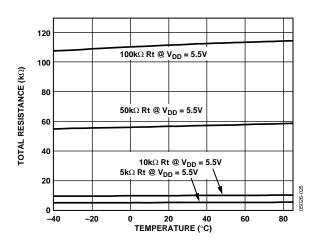

Figure 21. Total Resistance vs. Temperature

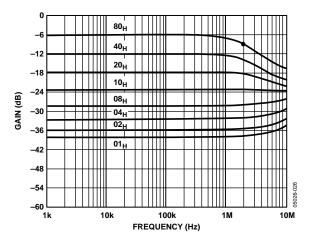

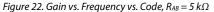

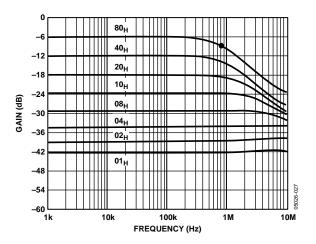

Figure 23. Gain vs. Frequency vs. Code,  $R_{AB} = 10 k\Omega$

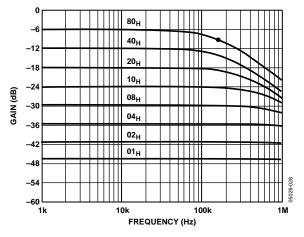

Figure 24. Gain vs. Frequency vs. Code,  $R_{AB} = 50 k\Omega$

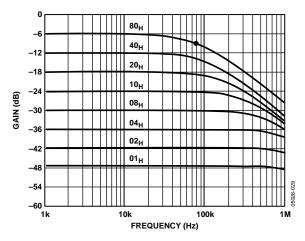

Figure 25. Gain vs. Frequency vs. Code,  $R_{AB} = 100 \, k\Omega$

Figure 26. -3 dB Bandwidth @ Code =  $0 \times 80$

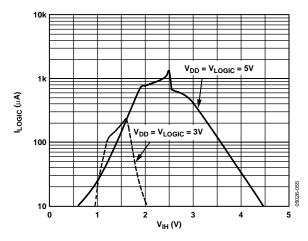

Figure 27. Logic Supply Current vs. Input Voltage

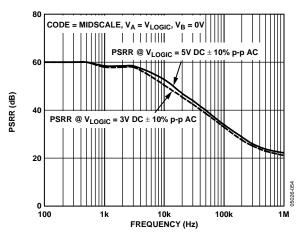

Figure 28. PSRR vs. Frequency

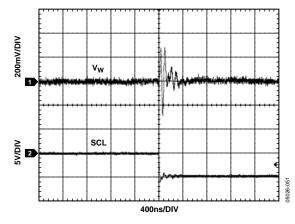

Figure 29. Digital Feedthrough

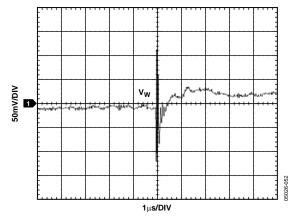

Figure 30. Midscale Glitch, Code 0×7F to 0×80

Figure 31. Large Signal Settling Time

### **TEST CIRCUITS**

Figure 32 through Figure 37 illustrate the test circuits that define the test conditions used in the product Specifications tables.

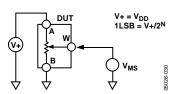

Figure 32. Test Circuit for Potentiometer Divider Nonlinearity Error (INL, DNL)

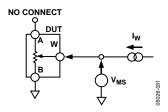

Figure 33. Test Circuit for Resistor Position Nonlinearity Error (Rheostat Operation; R-INL, R-DNL)

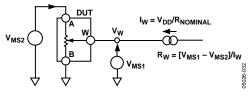

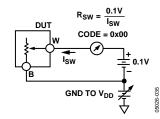

Figure 34. Test Circuit for Wiper Resistance

Figure 35. Test Circuit for Power Supply Sensitivity (PSS, PSSR)

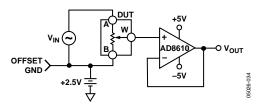

Figure 36. Test Circuit for Gain vs. Frequency

Figure 37. Test Circuit for Common-Mode Leakage Current

### THEORY OF OPERATION

The AD5259 is a 256-position digitally-controlled variable resistor (VR) device. EEPROM is pre-loaded at midscale from the factory, and initial power-up is, accordingly, at midscale.

### **PROGRAMMING THE VARIABLE RESISTOR**

#### **Rheostat Operation**

The nominal resistance ( $R_{AB}$ ) of the RDAC between Terminal A and Terminal B is available in 5 k $\Omega$ , 10 k $\Omega$ , 50 k $\Omega$ , and 100 k $\Omega$ . The nominal resistance of the VR has 256 contact points accessed by the wiper terminal. The 8-bit data in the RDAC latch is decoded to select one of 256 possible settings.

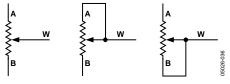

Figure 38. Rheostat Mode Configuration

The general equation determining the digitally programmed output resistance between Wiper W and Terminal B is

$$R_{WB}(D) = \frac{D}{256} \times R_{AB} + 2 \times R_{W}$$

(1)

where:

*D* is the decimal equivalent of the binary code loaded in the 8-bit RDAC register.

$R_{AB}$  is the end-to-end resistance.

$R_W$  is the wiper resistance contributed by the ON resistance of each internal switch.

Figure 39. AD5259 Equivalent RDAC Circuit

In the zero-scale condition, there is a relatively low value finite wiper resistance. Care should be taken to limit the current flow between Wiper W and Terminal B in this state to a maximum pulse current of no more than 20 mA. Otherwise, degradation or destruction of the internal switch contact can occur.

Similar to the mechanical potentiometer, the resistance of the RDAC between Wiper W and Terminal A produces a digitally controlled complementary resistance,  $R_{WA}$ . The resistance value setting for  $R_{WA}$  starts at a maximum value of resistance and decreases as the data loaded in the latch increases in value. The general equation for this operation is

$$R_{WA}(D) = \frac{256 - D}{256} \times R_{AB} + 2 \times R_{W}$$

(2)

Typical device-to-device matching is process lot dependent and may vary by up to  $\pm 30\%$ . For this reason, resistance tolerance is stored in the EEPROM, enabling the user to know the actual R<sub>AB</sub> within 0.1%.

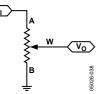

### PROGRAMMING THE POTENTIOMETER DIVIDER Voltage Output Operation

The digital potentiometer easily generates a voltage divider at Wiper W to Terminal B and Wiper W to Terminal A proportional to the input voltage at Terminal A to Terminal B. Unlike the polarity of  $V_{DD}$  to GND, which must be positive, voltage across Terminal A to Terminal B, Wiper W to Terminal A, and Wiper W to Terminal B can be at either polarity.

Figure 40. Potentiometer Mode Configuration

If ignoring the effect of the wiper resistance for approximation, connecting the A terminal to 5 V and the B terminal to ground produces an output voltage at Wiper W to Terminal B starting at 0 V up to 1 LSB less than 5 V. The general equation defining the output voltage at V<sub>w</sub> with respect to ground for any valid input voltage applied to Terminal A and Terminal B is

$$V_W(D) = \frac{D}{256} V_A + \frac{256 - D}{256} V_B \tag{3}$$

A more accurate calculation, which includes the effect of wiper resistance,  $V_{\rm W},$  is

$$V_{W}(D) = \frac{R_{WB}(D)}{R_{AB}} V_{A} + \frac{R_{WA}(D)}{R_{AB}} V_{B}$$

(4)

Operation of the digital potentiometer in the divider mode results in a more accurate operation over temperature. Unlike the rheostat mode, the output voltage is dependent mainly on the ratio of the Internal Resistors  $R_{WA}$  and  $R_{WB}$  and not the absolute values.

### I<sup>2</sup>C-COMPATIBLE INTERFACE

The master initiates data transfer by establishing a start condition, which is when a high-to-low transition on the SDA line occurs while SCL is high (see Figure 4). The next byte is the slave address byte, which consists of the slave address (first 7 bits) followed by an  $R/\overline{W}$  bit (see Table 6). When the  $R/\overline{W}$  bit is high, the master reads from the slave device. When the  $R/\overline{W}$ bit is low, the master writes to the slave device.

The slave address of the part is determined by two configurable address pins, Pin AD0 and Pin AD1. The state of these two pins is registered upon power-up and decoded into a corresponding  $I^2C$  7-bit address (see Table 5). The slave address corresponding to the transmitted address bits responds by pulling the SDA line low during the ninth clock pulse (this is termed the slave acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to, or read from, its serial register.

### WRITING

In the write mode, the last bit (R/W) of the slave address byte is logic low. The second byte is the instruction byte. The first three bits of the instruction byte are the command bits (see Table 6). The user must choose whether to write to the RDAC register, EEPROM register, or activate the software write protect (see Table 7 to Table 10). The final five bits are all zeros (see Table 13 to Table 14). The slave again responds by pulling the SDA line low during the ninth clock pulse.

The final byte is the data byte MSB first. With the write protect mode, data is not stored; rather, a logic high in the LSB enables write protect. Likewise, a logic low disables write protect. The slave again responds by pulling the SDA line low during the ninth clock pulse.

### STORING/RESTORING

In this mode, only the address and instruction bytes are necessary. The last bit  $(R/\overline{W})$  of the address byte is logic low. The first three bits of the instruction byte are the command bits (see Table 6). The two choices are transfer data from RDAC to EEPROM (store), or from EEPROM to RDAC (restore). The final five bits are all zeros (see Table 13 to Table 14).

### READING

Assuming the register of interest was not just written to, it is necessary to write a dummy address and instruction byte. The instruction byte will vary depending on whether the data that is wanted is the RDAC register, EEPROM register, or tolerance register (see Table 11 and Table 16).

After the dummy address and instruction bytes are sent, a repeat start is necessary. After the repeat start, another address byte is needed, except this time the  $R/\overline{W}$  bit is logic high. Following this address byte is the readback byte containing the information requested in the instruction byte. Read bits appear on the negative edges of the clock.

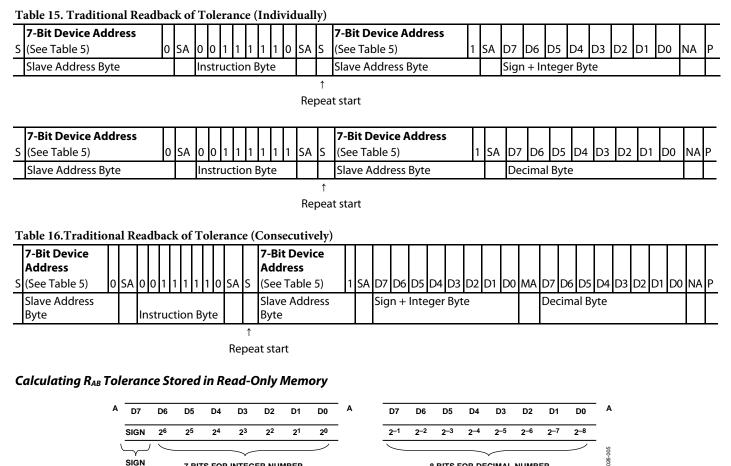

The tolerance register can be read back individually (see Table 15) or consecutively (see Table 16). Refer to the Read Modes section for detailed information on the interpretation of the tolerance bytes.

After all data bits have been read or written, a stop condition is established by the master. A stop condition is defined as a low-tohigh transition on the SDA line while SCL is high. In write mode, the master pulls the SDA line high during the tenth clock pulse to establish a stop condition (see Figure 46). In read mode, the master issues a no acknowledge for the ninth clock pulse (that is, the SDA line remains high). The master then brings the SDA line low before the tenth clock pulse, and then raises SDA high to establish a stop condition (see Figure 47).

A repeated write function gives the user flexibility to update the RDAC output a number of times after addressing and instructing the part only once. For example, after the RDAC has acknowledged its slave address and instruction bytes in the write mode, the RDAC output is updated on each successive byte until a stop condition is received. If different instructions are needed, the write/read mode has to start again with a new slave address, instruction, and data byte. Similarly, a repeated read function of the RDAC is also allowed.

### I<sup>2</sup>C-COMPATIBLE FORMAT

The following generic, write, read, and store/restore control registers for the AD5259 all refer to the device addresses listed in Table 5; the mode/condition reference key (S, P, SA, MA, NA,  $\overline{W}$ , R, and X) is listed below.

**P** = Stop Condition

**SA** = Slave Acknowledge

**MA** = Master Acknowledge

**NA** = No Acknowledge

$\overline{\mathbf{W}} = Write$

$\mathbf{R} = \text{Read}$

$\mathbf{X} =$ Don't Care

### **GENERIC INTERFACE**

#### **Table 6. Generic Interface Format**

|   | 7-Bit Device Address |     |    |       |       |       |    |    |    |    |    |    |      |      |    |    |    |    |    |    |    | Γ |

|---|----------------------|-----|----|-------|-------|-------|----|----|----|----|----|----|------|------|----|----|----|----|----|----|----|---|

| S | (See Table 5)        | R/W | SA | C2    | C1    | C0    | A4 | A3 | A2 | A1 | A0 | SA | D7   | D6   | D5 | D4 | D3 | D2 | D1 | D0 | SA | Ρ |

|   | Slave Address Byte   |     |    | Instr | uctio | on By | te |    |    |    |    |    | Data | Byte |    |    |    |    |    |    |    | Γ |

#### Table 7. RDAC-to-EEPROM Interface Command Descriptions

| C2 | C1 | C0 | Command Description                                                      |

|----|----|----|--------------------------------------------------------------------------|

| 0  | 0  | 0  | Operation Between Interface and RDAC.                                    |

| 0  | 0  | 1  | Operation Between Interface and EEPROM.                                  |

| 0  | 1  | 0  | Operation Between Interface and Write Protection Register. See Table 10. |

| 1  | 0  | 0  | NOP.                                                                     |

| 1  | 0  | 1  | Restore EEPROM to RDAC.                                                  |

| 1  | 1  | 0  | Store RDAC to EEPROM.                                                    |

### WRITE MODES

#### Table 8. Writing to RDAC Register

|    | 7-Bit Device Address               |      |                  |      |       |       |     |   |   |   |   |      |           |        |    |    |    |    |    |    |    |   |

|----|------------------------------------|------|------------------|------|-------|-------|-----|---|---|---|---|------|-----------|--------|----|----|----|----|----|----|----|---|

| 5  | (See Table 5)                      | 0    | SA               | 0    | 0     | 0     | 0   | 0 | 0 | 0 | 0 | SA   | D7        | D6     | D5 | D4 | D3 | D2 | D1 | D0 | SA | Ρ |

|    | Slave Address Byte                 |      |                  | Inst | ructi | on By | /te |   |   |   |   |      | Data      | a Byte | 5  |    |    |    |    | -  |    |   |

| Га | ble 9. Writing to EEPROM Regist    | er   |                  |      |       |       |     |   |   |   |   |      |           |        |    |    |    |    |    |    |    |   |

|    | 7-Bit Device Address               |      |                  |      |       |       |     |   |   |   |   |      |           |        |    |    |    |    |    | Γ  |    | Т |

| S  | (See Table 5)                      | 0    | SA               | 0    | 0     | 1     | 0   | 0 | 0 | 0 | 0 | SA   | D7        | D6     | D5 | D4 | D3 | D2 | D1 | D0 | SA | Ρ |

|    | Slave Address Byte                 |      |                  | Inst | ructi | on By | /te |   |   |   |   |      | Data Byte |        |    |    |    |    |    |    |    | Т |

| Га | ble 10. Activating/Deactivating So | ftwa | re W             | rite | Prot  | ect   |     |   |   |   |   |      |           |        |    |    |    |    |    |    |    |   |

|    | 7-Bit Device Address               |      |                  |      |       |       |     |   |   |   |   |      |           |        |    |    |    |    |    |    |    |   |

| s  | (See Table 5)                      | 0    | SA               | 0    | 1     | 0     | 0   | 0 | 0 | 0 | 0 | SA   | 0         | 0      | 0  | 0  | 0  | 0  | 0  | WP | SA | Ρ |

|    | Slave Address Byte                 |      | Instruction Byte |      |       |       |     |   |   |   |   | Data | a Byte    | ۔<br>د |    | -  | -  | -  | -  | Ī  | T  |   |

In order to activate the write protection mode, the WP bit in Table 10 must be logic high. To deactivate the write protection, the command must be sent again, except with the WP in logic zero state. WP is reset to the deactivated mode if power is cycled off and on.

AD1 and AD0 are two-state address pins.

#### Table 5. Device Address Lookup

| Tuble 5. Device In | autess Lookup   |                                 |

|--------------------|-----------------|---------------------------------|

| AD1 Address Pin    | AD0 Address Pin | I <sup>2</sup> C Device Address |

| 0                  | 0               | 0011000                         |

| 1                  | 0               | 0011010                         |

| 0                  | 1               | 1001100                         |

| 1                  | 1               | 1001110                         |

### **READ MODES**

Read modes are referred to as traditional because the first two bytes for all three cases are dummy bytes, which function to place the pointer towards the correct register; this is the reason for the repeat start. Theoretically, this step can be avoided if the user reads a register previously written to. For example, if the EEPROM was just written to, the user can then skip the two dummy bytes and proceed directly to the slave address byte, followed by the EEPROM readback data.

### Table 11. Traditional Readback of RDAC Register Value

|   | 7-Bit Device Address |      |     |       |     |     |     |    |   | 7-Bit Device Address |   |    |     |      |       |      |    |    |    |    |    | Γ |

|---|----------------------|------|-----|-------|-----|-----|-----|----|---|----------------------|---|----|-----|------|-------|------|----|----|----|----|----|---|

| S | (See Table 5)        | 0 SA | 0   | 0 0   | 0 0 | 0 0 | 0 0 | SA | S | (See Table 5) 1      | 1 | SA | D7  | D6   | D5    | D4   | D3 | D2 | D1 | D0 | NA | Ρ |

|   | Slave Address Byte   |      | Ins | truct | ion | Byt | e   |    |   | Slave Address Byte   |   |    | Rea | d Ba | nck D | Data |    |    |    |    |    | Γ |

|   |                      |      |     |       |     |     |     |    | 1 |                      |   |    |     |      |       |      |    |    |    |    |    |   |

Repeat start

#### Table 12. Traditional Readback of Stored EEPROM Value

|   | 7-Bit Device Address |    |     |     |     |     |     |     |   |   |    |          |   | 7-Bit Device Address |   |    |     |      |      |      |    |    |    |    |    |

|---|----------------------|----|-----|-----|-----|-----|-----|-----|---|---|----|----------|---|----------------------|---|----|-----|------|------|------|----|----|----|----|----|

| S | (See Table 5) 0      | SA | 0   | 0   | 1   | 0   | 0   | 0   | 0 | 0 | SA | <u>،</u> | S | (See Table 5)        | 1 | SA | D7  | D6   | D5   | D4   | D3 | D2 | D1 | D0 | NA |

|   | Slave Address Byte   |    | Ins | trι | ıct | ior | n B | yte | j |   |    |          |   | Slave Address Byte   |   |    | Rea | d Ba | ck D | )ata |    |    |    |    |    |

↑ Repeat start

### **STORE/RESTORE MODES**

#### Table 13. Storing RDAC Value to EEPROM

|   | 7-Bit Device Address |   |    |          |          |   |   |   |   |   |   |    |   |

|---|----------------------|---|----|----------|----------|---|---|---|---|---|---|----|---|

| S | (See Table 5)        | 0 | SA | 1        | 1        | 0 | 0 | 0 | 0 | 0 | 0 | SA | Р |

|   | Slave Address Byte   |   |    | Instruct | ion Byte |   |   |   |   |   |   |    |   |

#### Table 14. Restoring EEPROM to RDAC

|   | 7-Bit Device Address |    |           |         |   |   |   |   |   |   |    |   |

|---|----------------------|----|-----------|---------|---|---|---|---|---|---|----|---|

| S | (See Table 5)        | SA | 1         | 0       | 1 | 0 | 0 | 0 | 0 | 0 | SA | Р |

|   | Slave Address Byte   |    | Instructi | on Byte |   |   |   |   |   |   |    |   |

### **TOLERANCE READBACK MODES**

Figure 41. Format of Stored Tolerance in Sign Magnitude Format with Bit Position Descriptions. (Unit is Percent. Only Data Bytes are Shown.)

The AD5259 features a patented RAB tolerance storage in the nonvolatile memory. The tolerance is stored in the memory during factory production and can be read by users at any time. The knowledge of stored tolerance allows users to accurately calculate RAB. This feature is valuable for precision, rheostat mode, and open-loop applications where knowledge of absolute resistance is critical.

7 BITS FOR INTEGER NUMBER

The stored tolerance resides in the read-only memory and is expressed as a percentage. The tolerance is stored in two memory location bytes in sign magnitude binary form (see Figure 41).

The two EEPROM address bytes are 11110 (sign + integer) and 11111 (decimal number). The two bytes can be individually accessed with two separate commands (see Table 15). Alternatively, readback of the first byte followed by the second byte can be done in one command (see Table 16). In the latter case, the memory pointer will automatically increment from the first to the second EEPROM location (increments from 11110 to 11111) if read consecutively.

In the first memory location, the MSB is designated for the sign (0 = + and 1 = -) and the seven LSBs are designated for the integer portion of the tolerance. In the second memory location, all eight data bits are designated for the decimal portion of tolerance. Note the decimal portion has a limited accuracy of only 0.1%. For example, if the rated  $R_{AB} = 10 \text{ k}\Omega$ and the data readback from Address 11110 shows 0001 1100, and Address 11111 shows 0000 1111, then the tolerance can be calculated as

MSB: 0 = +Next 7 MSB: 001 1100 = 28 8 LSB: 0000 1111 =  $15 \times 2^{-8} = 0.06$ Tolerance = +28.06%*Rounded Tolerance* = +28.1% and therefore,  $R_{AB\_ACTUAL} = 12.810 \text{ k}\Omega$

8 BITS FOR DECIMAL NUMBER

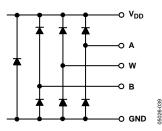

# ESD PROTECTION OF DIGITAL PINS AND RESISTOR TERMINALS

The AD5259  $V_{DD}$ ,  $V_{LOGIC}$ , and GND power supplies define the boundary conditions for proper 3-terminal and digital input operation. Supply signals present on Terminal A, Terminal B, and Terminal W that exceed  $V_{DD}$  or GND are clamped by the internal forward biased ESD protection diodes (see Figure 42). Digital Input SCL and Digital Input SDA are clamped by ESD protection diodes with respect to  $V_{LOGIC}$  and GND as shown in Figure 43.

Figure 42. Maximum Terminal Voltages Set by VDD and GND

Figure 43. Maximum Terminal Voltages Set by VLOGIC and GND

### **POWER-UP SEQUENCE**

Because the ESD protection diodes limit the voltage compliance at Terminal A, Terminal B, and Terminal W (see Figure 42), it is important to power GND/V<sub>DD</sub>/V<sub>LOGIC</sub> before applying any voltage to Terminal A, Terminal B, and Terminal W; otherwise, the diode is forward biased, so the V<sub>DD</sub> and V<sub>LOGIC</sub> are powered unintentionally and may affect the user's circuit. The ideal powerup sequence is in the following order: GND, V<sub>DD</sub>, V<sub>LOGIC</sub>, digital inputs, and then V<sub>A</sub>, V<sub>B</sub>, V<sub>W</sub>. The relative order of powering V<sub>A</sub>, V<sub>B</sub>, V<sub>W</sub>, and the digital inputs is not important as long as they are powered after GND/V<sub>DD</sub>/V<sub>LOGIC</sub>.

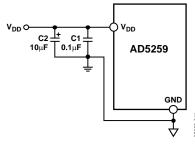

### LAYOUT AND POWER SUPPLY BYPASSING

It is good practice to use compact, minimum lead length layout design. The leads to the inputs should be as direct as possible with minimum conductor length. Ground paths should have low resistance and low inductance.

Similarly, it is also good practice to bypass the power supplies with quality capacitors for optimum stability. Supply leads to the device should be bypassed with disc or chip ceramic capacitors of 0.01  $\mu$ F to 0.1  $\mu$ F. Low ESR 1  $\mu$ F to 10  $\mu$ F tantalum or electrolytic capacitors should also be applied at the supplies to minimize any transient disturbance and low frequency ripple (see Figure 44). The digital ground should also be joined remotely to the analog ground at one point to minimize the ground bounce.

Figure 44. Power Supply Bypassing

### **MULTIPLE DEVICES ON ONE BUS**

The AD5259 has two configurable address pins, Pin AD0 and Pin AD1. The state of these two pins is registered upon powerup and decoded into a corresponding I<sup>2</sup>C-compatible 7-bit address (see Table 5). This allows up to four devices on the bus to be written to or read from independently.

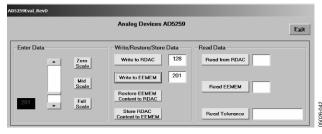

### **EVALUATION BOARD**

An evaluation board, with all necessary software, is available to program the AD5259 from any PC running Windows<sup>®</sup> 98/ 2000/ XP. The graphical user interface, as shown in Figure 45, is straightforward and easy to use. More detailed information is available in the board's user manual.

Figure 45. AD5259 Evaluation Board Software

# **DISPLAY APPLICATIONS**

### CIRCUITRY

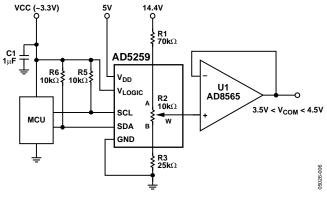

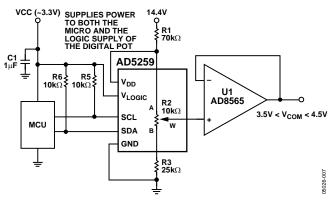

A special feature of the AD5259 is its unique separation of the  $V_{\text{LOGIC}}$  and  $V_{\text{DD}}$  supply pins. The separation provides greater flexibility in applications that do not always provide needed supply voltages.

In particular, LCD panels often require a  $V_{COM}$  voltage in the range of 3 V to 5 V. The circuit in Figure 46 is the rare exception in which a 5 V supply is available to power the digital potentiometer.

Figure 46. V<sub>COM</sub> Adjustment Application

In the more common case shown in Figure 47, only analog 14.4 V and digital logic 3.3 V supplies are available. By placing discrete resistors above and below the digital potentiometer,  $V_{DD}$  can now be tapped off the resistor string itself. Based on the chosen resistor values, the voltage at  $V_{DD}$  in this case equals 4.8 V, allowing the wiper to be safely operated all the way up to 4.8 V. The current draw of  $V_{DD}$  will not affect that node's bias because it is only on the order of microamps.  $V_{LOGIC}$  is tied to the MCU's 3.3 V digital supply because  $V_{LOGIC}$  will draw the 35 mA which is needed when writing to the EEPROM. It would be impractical to try and source 35 mA through the 70 k $\Omega$  resistor, therefore,  $V_{LOGIC}$  is not connected to the same node as  $V_{DD}$ .

For this reason,  $V_{LOGIC}$  and  $V_{DD}$  are provided as two separate supply pins that can either be tied together or treated independently;  $V_{LOGIC}$  supplying the logic/EEPROM with power, and  $V_{DD}$  biasing up the A, B, and W terminals for added flexibility.

Figure 47. Circuitry When a Separate Supply is Not Available for  $V_{DD}$

For a more detailed look at this application, refer to the article, "Simple VCOM Adjustment uses any Logic Supply Voltage" in the September 30, 2004 issue of *EDN* magazine.

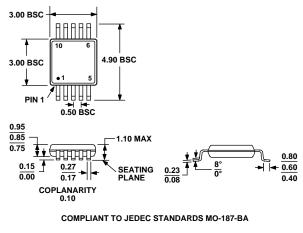

### **OUTLINE DIMENSIONS**

Figure 48. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

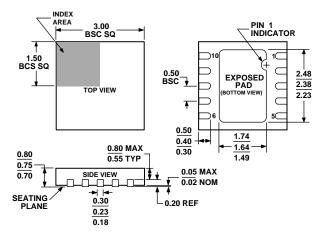

Figure 49. 10-Lead Lead Frame Chip Scale Package [LFCSP\_WD]

3 mm × 3 mm Body, Very Very Thin, Dual Lead (CP-10-9) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                   | <b>R</b> <sub>AB</sub> (Ω) | Temperature    | Package Description | Package Option | Branding |

|-------------------------|----------------------------|----------------|---------------------|----------------|----------|

| AD5259BRMZ51            | 5 k                        | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4P      |

| AD5259BRMZ5-R71         | 5 k                        | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4P      |

| AD5259BCPZ5-R71         | 5 k                        | -40°C to +85°C | 10-Lead LFCSP_WD    | CP-10-9        | D4P      |

| AD5259BRMZ101           | 10 k                       | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4Q      |

| AD5259BRMZ10-R71        | 10 k                       | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4Q      |

| AD5259BCPZ10-R71        | 10 k                       | -40°C to +85°C | 10-Lead LFCSP_WD    | CP-10-9        | D4Q      |

| AD5259BRMZ501           | 50 k                       | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4R      |

| AD5259BRMZ50-R71        | 50 k                       | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4R      |

| AD5259BCPZ50-R71        | 50 k                       | -40°C to +85°C | 10-Lead LFCSP_WD    | CP-10-9        | D4R      |

| AD5259BRMZ1001          | 100 k                      | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4S      |

| AD5259BRMZ100-R71       | 100 k                      | -40°C to +85°C | 10-Lead MSOP        | RM-10          | D4S      |

| AD5259BCPZ100-R71       | 100 k                      | -40°C to +85°C | 10-Lead LFCSP_WD    | CP-10-9        | D4S      |

| AD5259EVAL <sup>2</sup> |                            |                | Evaluation Board    |                |          |

$^{1}$  Z = Pb-free part.

$^2$  The evaluation board is shipped with the 10 k $\Omega$  R<sub>AB</sub> resistor option; however, the board is compatible with all available resistor value options.

# NOTES

# NOTES

### NOTES

Purchase of licensed I<sup>2</sup>C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective companies. D05026-0-7/05(A)

www.analog.com

Rev. A | Page 24 of 24